想一想还是多写点东西才好,不然很快就忘记了。

前些天一个同学问了一个问题,问题如下:

reg [9:0]a; reg [9:0]b; reg [9:0]c; reg [11:0]d; ……………… d<=a+b+c;

仿真的时候,a,b,c每一个位都是全1,发现,d[10]为1,不知道为什么,他想的是,加数是10位的,三个数相加,得到应该还是一个10位的加数,溢出不管,这样d[10]和d[11]应该是00才对。

我想了下很奇怪呀,然后觉得应该是在实现的时候进行了位扩充,然后才进行的加法。

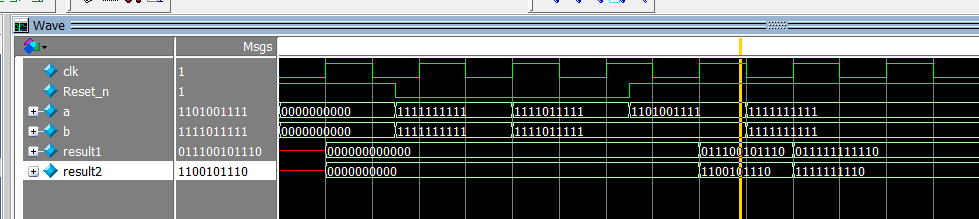

然后进行了仿真,两个加数为10为,结果为12位,当加数为全1时,结果真如想的那样,是进行了扩位后进行的加法。

如下所示:

正好今天在看《无线通信的MATLAB和FPGA实现》时,看到它怎么做加法。

书上内容如下:

reg [12:0] Adder_Out;

reg [11:0] Adder_In1,Adder_In2;

Adder_Out <= {Adder_In1[11],Adder_In1} + {Adder_In2[11],Adder_In2};

这里在处理加法时,对最高位进行扩展,即对符号位进行扩展。

按照实际来看,如果两个数是正数的话,不用人为的去进行符号位扩展也是可行的。

如果要做有符号位的加法,在定义时就需要定义为有符号数了。加法也是一样的,

故同样不用人为去做符号位扩展。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。